Philips Semiconductors

#### ABSTRACT

This report gives a description of the TDA8358JN1 version with a description of the TDA8358JN2 version together with application aspects.

© Philips Electronics N.V. 2002

All rights are reserved. Reproduction in whole or in part is prohibited without the prior consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

## **APPLICATION NOTE**

## Application information for TDA8358JN2 deflection output circuit with East - West amplifier

## AN10114-01

Author: Pieter van Oosten

System Application, Mainstream T.V. Solutions Consumer IC's Nijmegen The Netherlands

#### Keywords

TDA8358J Vertical deflection East - West amplifier Robust against flashover 90°, 110°

Date: June 2002

#### Summary

In this report you can find an application and product description of the DC coupled deflection output circuit with the type number TDA8358J. The TDA8358J is functional the same as the TDA8359J, but the TDA8358J has an additional east -west amplifier. A description is given of the differences between the TDA8358JN1 and TDA8358JN2. The application design procedure and the application investigations are given at the end of this report.

# TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

### CONTENTS

| 1.         | ΙΝΤ               | RODUCTION.                                                                         | 10   |

|------------|-------------------|------------------------------------------------------------------------------------|------|

| 1.1        |                   | Features.                                                                          | . 10 |

| 1.2        |                   | Ordering information.                                                              | . 10 |

| 1.3        |                   | Block diagram                                                                      | . 11 |

| 1.4        |                   | Pinning                                                                            | . 12 |

| 1.5        |                   | Quick reference data                                                               | .12  |

| <b>2</b> . | DE                | VICE DESCRIPTION AND APPLICATION INFORMATION                                       |      |

|            |                   |                                                                                    |      |

| 2.2        |                   | Application diagram                                                                |      |

| 2.3        |                   | Vertical amplifier                                                                 | . 17 |

| 2.4        |                   | Vertical input circuit                                                             | . 18 |

| 2          | 2.4.1             | Conversion resistors R <sub>CV1,2</sub> and measuring resistor R <sub>M</sub>      | .21  |

| 2          | 2.4.2             | Example of a single driven application with TDA8358J                               |      |

| 2.5        |                   | Feedback Circuit                                                                   | 24   |

| -          | 2.5.1             | Series resistor (R <sub>S</sub> )                                                  |      |

| -          |                   |                                                                                    | . 27 |

| 2.6        |                   | Vertical output stage                                                              | . 25 |

| 2.7        |                   | The flyback switch                                                                 | 20   |

|            | 2.7.1             | Adaptive control of the flyback switch                                             |      |

| 2          |                   |                                                                                    | . 51 |

| 2.8        |                   | Damping resistor R <sub>D1</sub> and damping resistor compensation circuit         | . 33 |

| 2          | 2.8.1             | Damping resistor R <sub>D1</sub>                                                   | . 33 |

| 2          | 2.8.2             | Damping resistor compensation circuit                                              |      |

| 2          | 2.8.3             | Calculation of the compensation resistor R <sub>CMP</sub>                          | . 34 |

|            |                   |                                                                                    |      |

| 2.9        |                   | Protection Circuits                                                                |      |

|            | 2.9.1             | High die temperature                                                               |      |

| 2          | 2.9.2             | Overvoltage output A                                                               | . 37 |

| 2.1        | 0                 | Vertical Guard Circuit                                                             | 38   |

| 2          | 2.10.1<br>circuit | Vertical guard with TDA935X/6X/8X/N2 / TDA955X/6X/8X family as TV signal processor |      |

|            | 2.10.2            |                                                                                    | . 41 |

| 2.1        | 1                 | Supplies                                                                           | . 44 |

| 2          | 2.11.1            | Calculation of the main supply $V_P$                                               |      |

| 2          | 2.11.2            | Calculation of the flyback supply                                                  | . 46 |

| 2.1        | 2                 | East - West Amplifier                                                              | . 49 |

# TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

| 2.12.1<br>2.12.2     |                            | Power calculation of the East - West stage<br>Feedback resistor calculation                                                                                 |          |  |  |  |

|----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| 2.13                 | 3                          | Heatsink calculation                                                                                                                                        | 52       |  |  |  |

| <b>2.14</b> . 2.14.1 |                            | Junction/die peak temperature check<br>Equivalent thermal resistance network.                                                                               |          |  |  |  |

| 2.1                  | 5                          | SOAR behaviour output                                                                                                                                       | 58       |  |  |  |

|                      | .16.1                      | Power dissipation of the vertical output stage                                                                                                              | 59       |  |  |  |

|                      | .16.2<br>.16.3             |                                                                                                                                                             |          |  |  |  |

| 2.17                 |                            | Flash-over.                                                                                                                                                 |          |  |  |  |

|                      | .17.1<br>.17.2             | Flash-over simulation6<br>Flashover behaviour of TDA8358J <u>N2</u> 6                                                                                       | 51<br>51 |  |  |  |

| 2.18                 | 8                          | ESD-gun test                                                                                                                                                | 52       |  |  |  |

| 2.19                 | Э                          | EMC behaviour                                                                                                                                               | 33       |  |  |  |

| 2.20                 | D                          | mproved temperature coefficient in TDA8358JN264                                                                                                             |          |  |  |  |

| 2.21                 | 1                          | /ertical compressed scan with TDA8358J64                                                                                                                    |          |  |  |  |

| 2.22                 | 2                          | Application design procedure of the TDA8358J.                                                                                                               | 6        |  |  |  |

| 3                    | <b>DIF</b><br>.1.1<br>.1.2 | FERENCES BETWEEN N1 AND N2                                                                                                                                  | 69       |  |  |  |

| 3.2                  | . 1.2                      | ESD-gun test                                                                                                                                                |          |  |  |  |

| 3.3                  |                            | Improved temperature coefficient in TDA8358JN2                                                                                                              |          |  |  |  |

|                      |                            |                                                                                                                                                             |          |  |  |  |

| 4.                   | EX                         | TENDED APPLICATION INVESTIGATION7                                                                                                                           |          |  |  |  |

| 4.1                  |                            | Introduction7                                                                                                                                               |          |  |  |  |

|                      | .2.1<br>.2.2               | Current peak at the end of flyback time.       7         Application without RC-filter.       7         Application with RC-filter 47 nF + 1.5 Ohm.       7 | 71       |  |  |  |

| 5.                   | AP                         | PENDIX7                                                                                                                                                     | '5       |  |  |  |

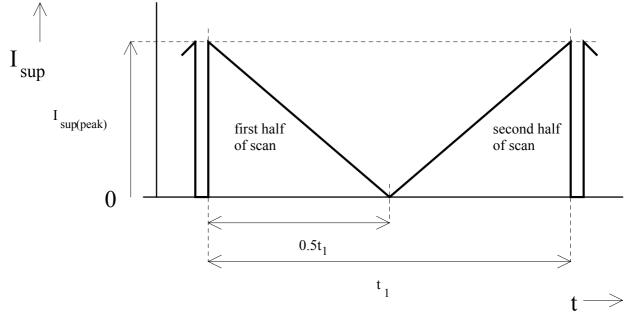

| 5.1                  |                            | Calculating the power P <sub>sup</sub>                                                                                                                      | 75       |  |  |  |

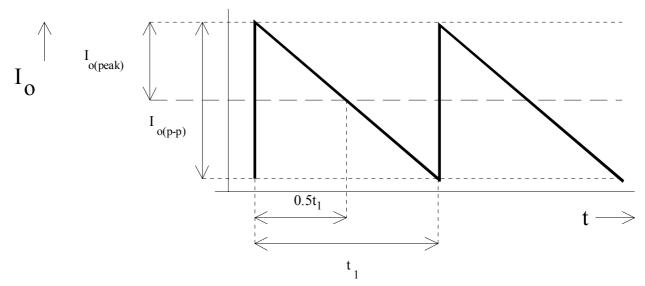

| 5.2                  |                            | Calculating the power dissipation $P_L$ 7                                                                                                                   | 77       |  |  |  |

| 6.                   | RE                         | FERENCES8                                                                                                                                                   | 0        |  |  |  |

## LIST OF FIGURES

| fig 1: Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| fig 2: Internal circuit configuration                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| fig 3: Application diagram                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| fig 4: Simplified block diagram of the vertical circuit.                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

| fig 5: Vertical drive output currents of the TDA935X/6X/8X / TDA955X/6X/8X family                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| fig 6: Input voltages on pin 1 INA and pin 2 INB of TDA8358J                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| fig 7: Differential input voltage (V <sub>INA</sub> -V <sub>INB</sub> )                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| fig 8: Input configuration.                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| fig 9: Interconnect between TDA935x/6x/8x / TDA955x/6x/8x and TDA8358J                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| fig 10: Example of a single driven application                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| fig 11: Feedback circuit                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

| fig 12: Output configuration TDA8358J                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| fig 13: Current path in first part of scan.                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| fig 14: Current path in second part of scan.                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| fig 15: Waveforms during scan                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| fig 16: Jump in output voltage                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| fig 17: Waveforms during flyback                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| fig 18: Current path in first part of flyback                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| fig 19: Current path in second part of flyback.                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

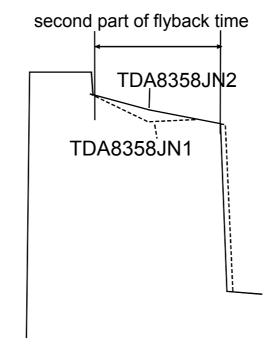

| fig 20: Small difference in output voltage (flyback pulse) between N1 and N2                                                                                                                                                                                                                                                                                                                                                               |                                                          |

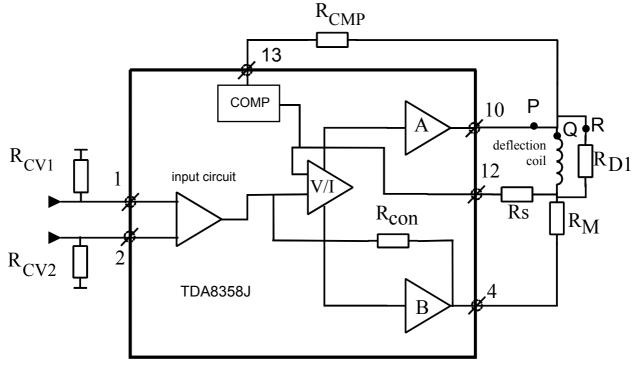

| fig 21: Damping resistor compensation.                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

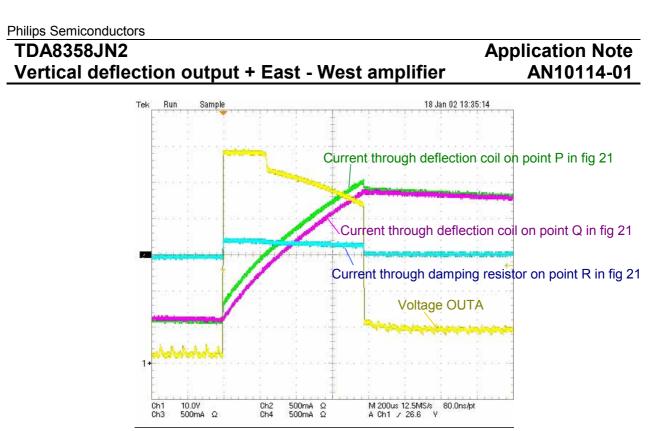

| fig 22: Current through deflection coil measured on point P, Q and R in fig 21                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| fig 23: Correct value of R <sub>CMP</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| fig 24: R <sub>CMP</sub> too low, current overshoot at start scan / end flyback, too much compensation                                                                                                                                                                                                                                                                                                                                     |                                                          |

| fig 25: R <sub>CMP</sub> too high, current undershoot at start scan / end flyback, too less compensation                                                                                                                                                                                                                                                                                                                                   |                                                          |

| fig 26: Guard application for TDA955X/6X/8X / TDA935X/6X/8X family                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

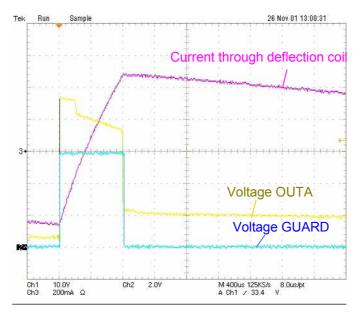

| fig 27: Scope picture of application with vertical guard on BLKIN.                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

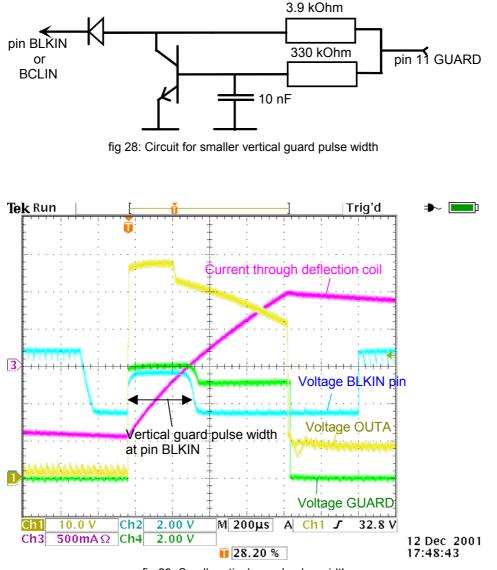

| fig 28: Circuit for smaller vertical guard pulse width                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| fig 29: Small vertical guard pulse width                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

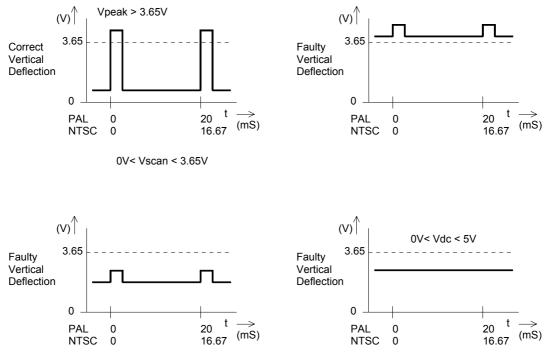

| fig 30: Guard pulses with TDA884X/5X family                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                       |

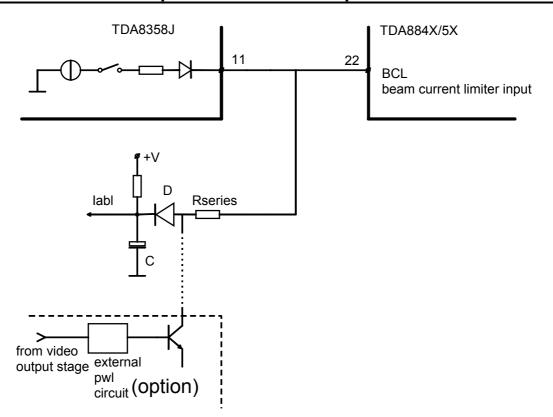

| fig 31: Guard with beam current application                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

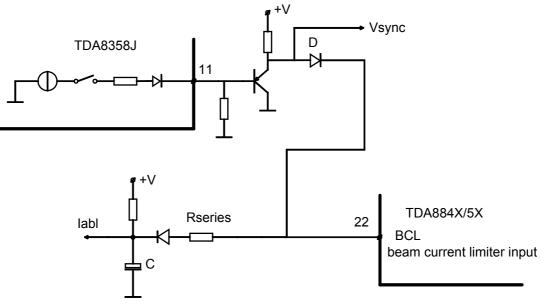

| fig 32: Application for guard pulse with high load                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

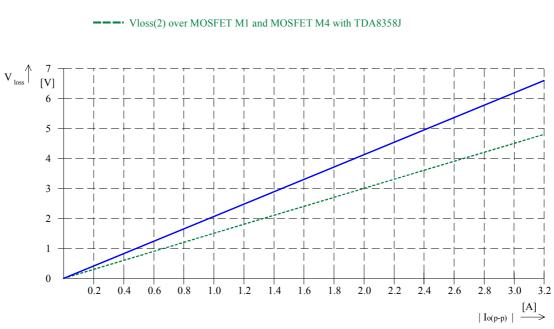

| fig 33: Voltage loss of the output stage.                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

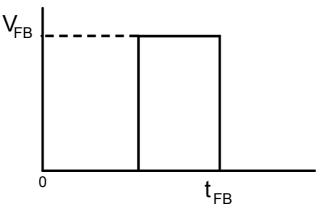

| fig 34: Simplified flyback time.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

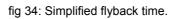

| fig 35: Block diagram E/W                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| fig 36: SOAR line of East - West output stage                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

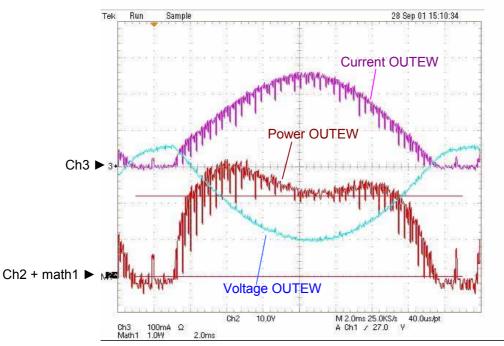

| fig 37: Current, Voltage and power of pin 8 OUTEW                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

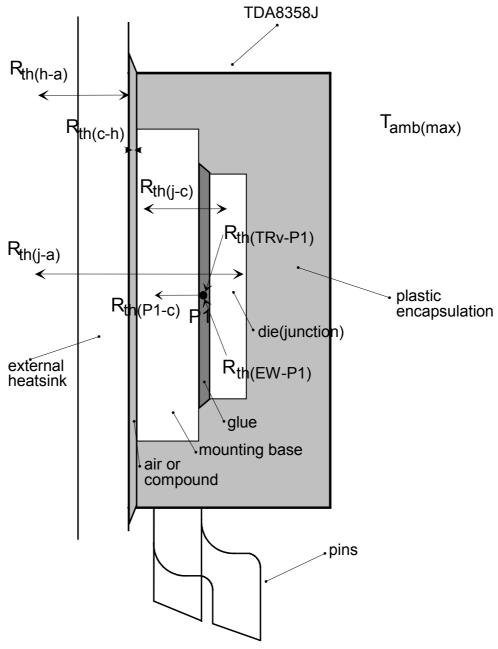

| fig 38: Construction of TDA8358J mounted on a heatsink                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

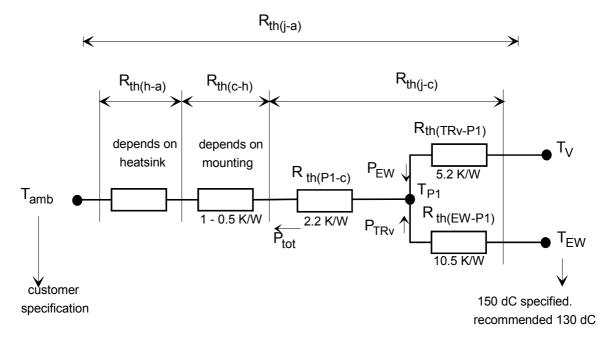

| fig 39: Equivalent thermal resistance network                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                       |

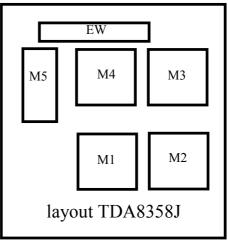

| fig 40: Layout of both output circuits of the TDA8358J                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

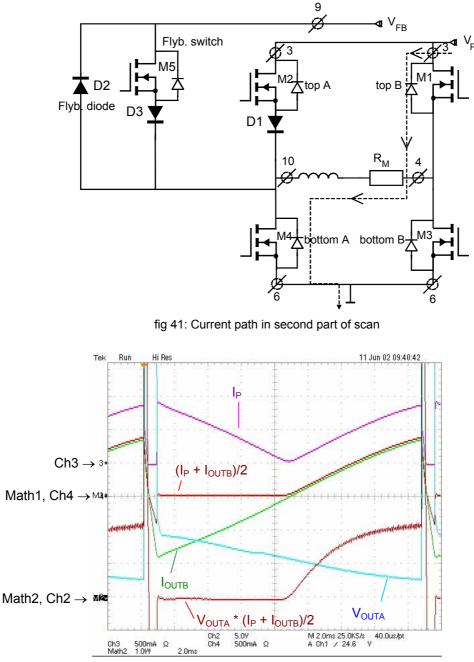

| fig 41: Current path in second part of scan                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                       |

| fig 42: Peak dissipation of M4                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br>56                                                 |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations                                                                                                                                                                                                                                                                                                                                                                                | 56<br>56<br>58                                           |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations<br>fig 44: Principle diagram                                                                                                                                                                                                                                                                                                                                                   | 56<br>56<br>58<br>59                                     |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection                                                                                                                                                                                                                                                                                          | 56<br>56<br>58<br>59<br>62                               |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.                                                                                                                                                                                                                              | 56<br>56<br>58<br>59<br>62<br>64                         |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.<br>fig 47: Vertical compressed scan with TDA8358J                                                                                                                                                                            | 56<br>58<br>59<br>62<br>64<br>65                         |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.<br>fig 47: Vertical compressed scan with TDA8358J<br>fig 48: Vertical compressed scan with TDA8358J with a zener diode on pin 4 OUTB to GND                                                                                  | 56<br>58<br>59<br>62<br>64<br>65                         |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.<br>fig 47: Vertical compressed scan with TDA8358J<br>fig 48: Vertical compressed scan with TDA8358J with a zener diode on pin 4 OUTB to GND<br>fig 49: Small difference in output voltage (flyback pulse) between N1 and N2. | 56<br>58<br>59<br>62<br>64<br>65<br>65<br>69             |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.<br>fig 47: Vertical compressed scan with TDA8358J<br>fig 48: Vertical compressed scan with TDA8358J with a zener diode on pin 4 OUTB to GND<br>fig 49: Small difference in output voltage (flyback pulse) between N1 and N2. | 56<br>58<br>62<br>62<br>64<br>65<br>65<br>69<br>70       |

| fig 42: Peak dissipation of M4<br>fig 43: Power limitations.<br>fig 44: Principle diagram.<br>fig 45: Recommended layout for flashover protection<br>fig 46: Recommended application for optimal suppression.<br>fig 47: Vertical compressed scan with TDA8358J<br>fig 48: Vertical compressed scan with TDA8358J with a zener diode on pin 4 OUTB to GND<br>fig 49: Small difference in output voltage (flyback pulse) between N1 and N2. | 56<br>58<br>59<br>62<br>62<br>65<br>65<br>65<br>69<br>70 |

# TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

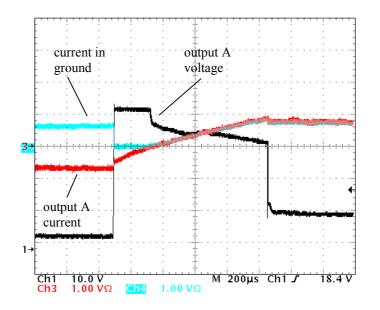

| fig 53: Flyback time of application without RC-filter on OUTA.                | 72 |

|-------------------------------------------------------------------------------|----|

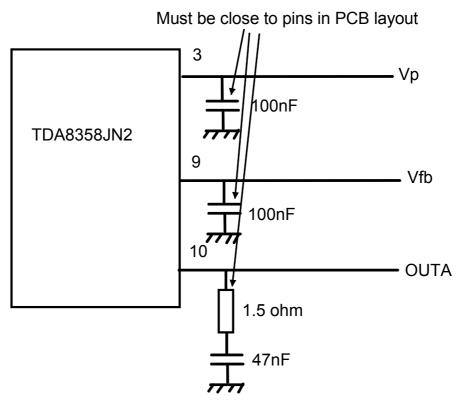

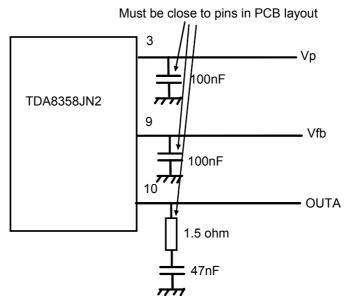

| fig 54: Application with RC-filter between OUTA and ground (47 nF + 1.5 Ohm). |    |

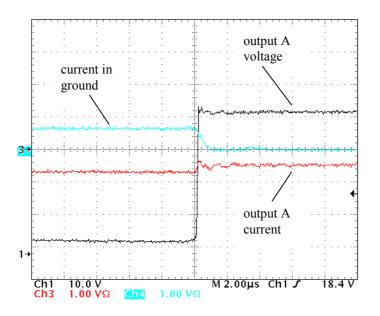

| fig 55: Application with RC-filter between OUTA and ground (47 nF + 1.5 Ohm). | 73 |

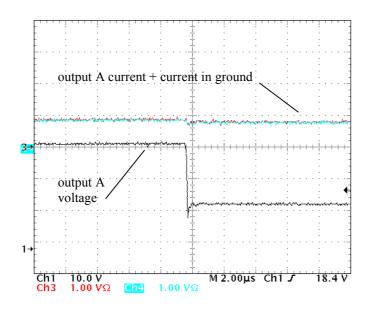

| fig 56: Application with RC-filter between OUTA and ground (47 nF + 1.5 Ohm). | 74 |

| fig 57: TDA8358J, current flow when discharging C                             | 74 |

| fig 58: Current of the supply                                                 | 75 |

| fig 59: Current through the deflection coil and $R_M$                         | 77 |

| Philips Semiconductors                             |                  |

|----------------------------------------------------|------------------|

| TDA8358JN2                                         | Application Note |

| Vertical deflection output + East - West amplifier | AN10114-01       |

#### TDA8358JN2 Vertical deflection output + East - West amplifier

#### 1. INTRODUCTION.

The TDA8358J is an integrated power circuit for use in 90° and 110° colour deflection systems. It contains a vertical deflection bridge output, which operates as a high efficiency class G system and can handle field frequencies from 25 to 200 Hz. The vertical deflection coil of a 4 : 3 as well a 16 : 9 picture tube can be connected to this vertical deflection device. Due to the bridge configuration a DC deflection output application can be designed with a single positive main supply of typical 12-Volt and a positive flyback supply of typical 45-Volt. (Depending on the vertical deflection coil data). The input configuration is symmetrical in order to have improved EMI behaviour.

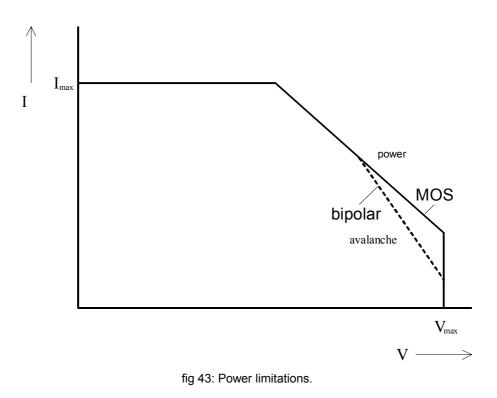

The integrated circuit is designed in a Low Voltage DMOS (LVDMOS) process that combines bipolar, CMOS and DMOS components. DMOS output transistors (MOSFETs) are used because of the absence of secondary breakdown, which gives a better SOAR performance. The internal circuits are designed in such way that only a few external components are needed to get a correct working application.

The TDA8358J is functional the same as the TDA8359J vertical deflection output stage. The TDA8358J differs in only one aspect from the TDA8359J; it has an additional East - West amplifier.

The TDA8358J is the successor for the TDA8350Q vertical deflection output stage with an east - west amplifier. There were two reasons to develop a successor. Reason number one was to have a better temperature distribution. This is done in a DMOS process in stead of Bipolar. Reason number two was to increase the output capacity of the East - West amplifier. The maximum East - West output voltage and maximum output current is increased.

#### 1.1 Features.

- Few external components required

- High efficiency fully DC coupled vertical bridge output circuit

- Short rise and fall time of the vertical flyback switch

- Temperature (thermal) protection circuit

- Blanking pulse generator (guard)

- Improved EMC performance due to differential inputs

- East West output stage

#### 1.2 Ordering information.

| Туре     | Package |                                              |         |  |  |

|----------|---------|----------------------------------------------|---------|--|--|

| Number   | Name    | Description                                  | Version |  |  |

| TDA8358J | DBS13P  | plastic DIL-bent-SIL power package; 13 leads | SOT141  |  |  |

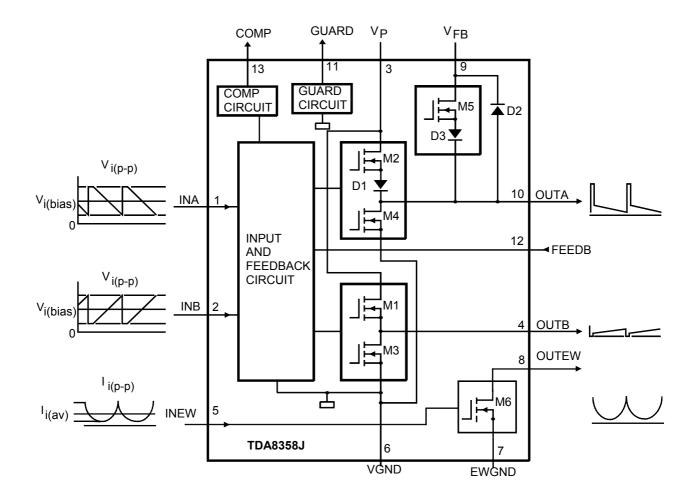

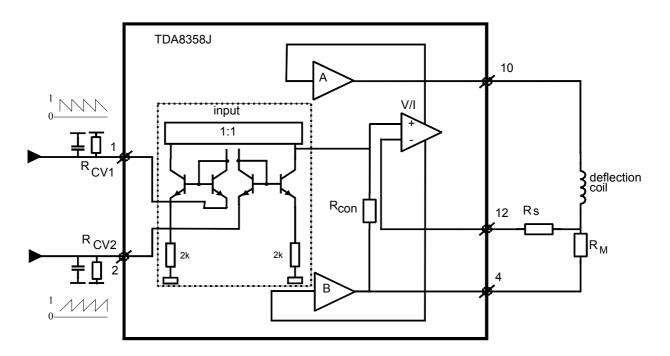

#### 1.3 Block diagram

fig 1: Block diagram.

| Philips Semiconductors                             |                  |

|----------------------------------------------------|------------------|

| TDA8358JN2                                         | Application Note |

| Vertical deflection output + East - West amplifier | AN10114-01       |

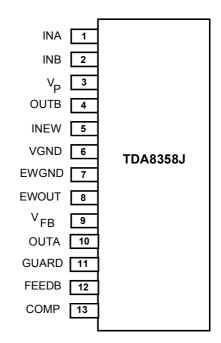

#### 1.4 Pinning

| Symbol          | Pin | Description                |

|-----------------|-----|----------------------------|

| INA 1           |     | vertical input (positive)  |

| INB             | 2   | vertical input (negative)  |

| VP              | 3   | supply voltage             |

| OUTB            | 4   | vertical output voltage B  |

| INEW            | 5   | East - West input voltage  |

| VGND 6          |     | Vertical ground            |

| EWGND 7         |     | East - West ground         |

| OUTEW           | 8   | East - West output voltage |

| V <sub>FB</sub> | 9   | flyback supply voltage     |

| OUTA            | 10  | vertical output voltage A  |

| GUARD           | 11  | guard output voltage       |

| FEEDB 12        |     | input measuring resistor   |

| COMP            | 13  | input compensation current |

#### 1.5 Quick reference data

| Symbol                   | Parameter                                            | Conditions             | Min.             | Тур. | Max. | Unit |

|--------------------------|------------------------------------------------------|------------------------|------------------|------|------|------|

| Supplies                 |                                                      |                        |                  |      |      |      |

| VP                       | supply voltage                                       |                        | 7.5              | 12   | 18   | V    |

| V <sub>FB</sub>          | flyback supply voltage                               |                        | 2xV <sub>P</sub> | 45   | 66   | V    |

| $I_{q(P)(av)}$           | average quiescent supply current                     | during scan            | -                | 10   | 15   | mA   |

| $I_{q(FB)(av)}$          | average quiescent flyback<br>supply current          | during scan            | -                | -    | 10   | mA   |

| P <sub>tot</sub>         | total power dissipation                              |                        | -                | -    | 15   | W    |

| Input and                | output                                               |                        |                  |      |      |      |

| V <sub>i(dif)(p-p)</sub> | differential input voltage (peak-<br>to- peak value) |                        | -                | 1000 | 1500 | mV   |

| I <sub>o(p-p)</sub>      | output current (peak-to-peak value)                  |                        | -                | -    | 3.2  | A    |

| Flyback s                | witch                                                |                        |                  |      |      |      |

| I <sub>o(peak)</sub>     | maximum (peak) output current                        | $t \le 1.5 \text{ ms}$ | -                | -    | ±1.8 | A    |

| East - Wes               | st amplifier                                         |                        | •                |      | •    |      |

| Vo                       | output voltage                                       |                        | -                | -    | 68   | V    |

| V <sub>I(bias)</sub>     | input bias voltage                                   |                        | 2                | -    | 3.2  | V    |

| I <sub>o</sub>           | output current                                       |                        | -                | -    | 750  | mA   |

| Symbol                                     | Parameter                                   | Conditions  | Min. | Тур. | Max. | Unit |

|--------------------------------------------|---------------------------------------------|-------------|------|------|------|------|

| Thermal data; in accordance with IEC 747-1 |                                             |             |      |      |      |      |

| T <sub>stg</sub>                           | storage temperature                         |             | -55  | -    | +150 | °C   |

| T <sub>amb</sub>                           | ambient temperature                         |             | -25  | -    | + 85 | С°   |

| Τ <sub>i</sub>                             | junction temperature                        |             | -    | -    | +150 | °C   |

| R <sub>th(j-c)</sub>                       | thermal resistance from junction to case    |             | -    | 4    | -    | K/W  |

| R <sub>th(j-a)</sub>                       | thermal resistance from junction to ambient | in free air | -    | 40   | -    | K/W  |

### TDA8358JN2 Vertical deflection output + East - West amplifier

### 2. DEVICE DESCRIPTION AND APPLICATION INFORMATION

#### 2.1 Internal pin configuration

| Pin | Symbol                  | Equivalent circuit  |

|-----|-------------------------|---------------------|

| 1   | INA                     |                     |

|     | NID.                    | 300 ohm<br>2k<br>2k |

| 2   | INB                     | 300 ohm<br>2K       |

| 3   |                         | (9)                 |

| 4 6 | OUTB<br>VGND            |                     |

| 9   | VGND<br>V <sub>FB</sub> |                     |

| 10  | OUTA                    |                     |

| 5   | INEW                    | 300.8               |

| 7   | EWGND                   |                     |

| 8   | OUTEW                   |                     |

| TDA8358JN2<br>Vertical deflection outp |        | Application Note<br>n output + East - West amplifier AN10114-01 |

|----------------------------------------|--------|-----------------------------------------------------------------|

| Pin                                    | Symbol | Equivalent circuit                                              |

| 11                                     | GUARD  |                                                                 |

|                                        |        |                                                                 |

| 12                                     | FEEDB  | 300 ohm                                                         |

(12)

13

MGL875

Ь

Ь

<u>300 Q</u>

COMP

13

fig 2: Internal circuit configuration

## TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

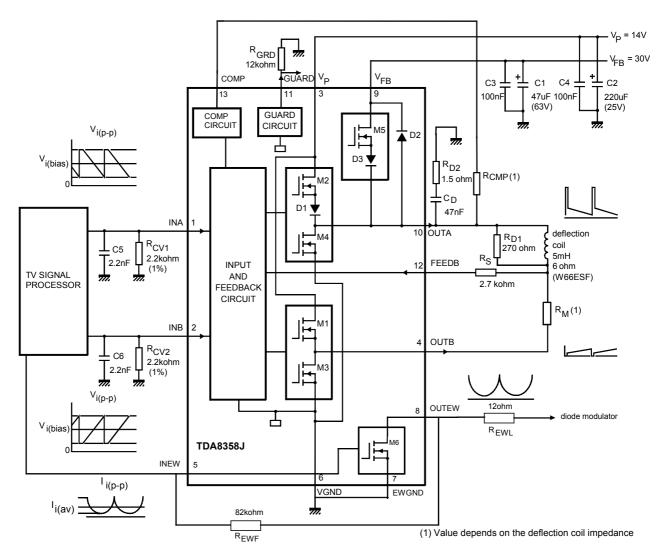

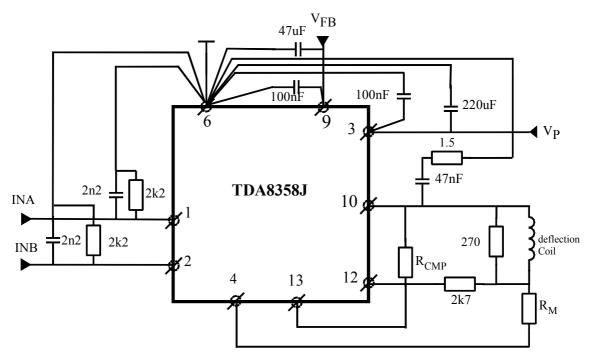

#### 2.2 Application diagram

fig 3: Application diagram.

The TDA8358J is a vertical drive circuit in a bridge configuration. The output amplifiers are driven in opposite phase.

When looking at the application diagram, the following components can be described in short terms (detailed information is given in the succeeding sections).

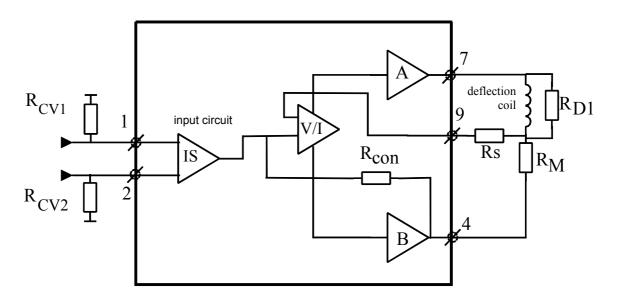

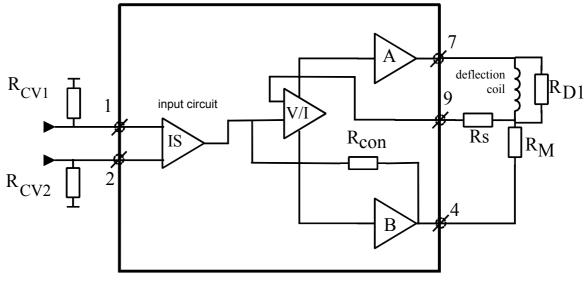

The input circuit of the TDA8358J is a differential voltage driven input. The external resistors  $R_{cv1}$  and  $R_{cv2}$  convert the output currents of the TV signal processor into input voltages. The differential input voltage is compared with the voltage across the measuring resistor  $R_M$  that provides feedback information. The deflection coil is connected between OUTA and resistor  $R_M$  and OUTB.

The damping resistor  $R_{D1}$  is connected across the deflection coil for HF loop stability. The damping resistor compensation, which consists of a resistor  $R_{CMP}$ , compensates current differences in the damping resistor during scan and flyback and assures a short settling time.

#### 2.3 Vertical amplifier

In many conventional deflection output circuits, the deflection coil must be AC coupled. This will require an expensive coupling capacitor of approximately 2200  $\mu$ F. Beside higher costs, the coupling capacitor can cause picture bounce after switching between channels on the TV set. This capacitor can be omitted in a DC coupled deflection output circuit.

The TDA8358J is a DC coupled deflection output circuit, which has no bounce effect during channel switching. Also DC-coupling enables easy DC-shifting of the picture. By using differential mode inputs the EMC immunity is improved. The deflection coil and the measuring resistor  $R_M$  are connected between the output amplifiers of the TDA8358J that is driven in opposite phase. See fig 3.

fig 4: Simplified block diagram of the vertical circuit.

Since the Input Stage (IS) is voltage driven, resistor  $R_{cv1}$  and  $R_{cv2}$  are used to convert the differential output current delivered by the TV signal processor (See fig 4). But TV signal processor circuits, which deliver an output voltage can also be used, in that case resistor  $R_{cv1}$  and  $R_{cv2}$  are not necessary.

The voltage across the internal conversion resistor  $R_{con}$  is compared with the output current through the deflection coil, measured as a voltage across the measuring resistor  $R_M$ , by means of a voltage current converter V/I. The output amplifiers A and B will be driven until both voltages are equal. This means that the deflection current is determined by the ratio of the input resistors  $R_{cv1,2}$  and the measuring resistor  $R_M$ .

The output current is adjustable up to 3.2  $A_{p-p}$  mainly by varying resistor  $R_M$ . The peak to peak input voltage should be as high as possible (maximum 1.5V) for having an optimal reducing of distortion on the input signals. The maximum input voltage (bias + peak voltage) is 1.6V. The minimum input voltage (bias - peak voltage) is 100 mV, however for an optimum linearity a minimum input voltage of 300 mV is recommended.

#### 2.4 Vertical input circuit

#### Pin 1 INA and pin 2 INB

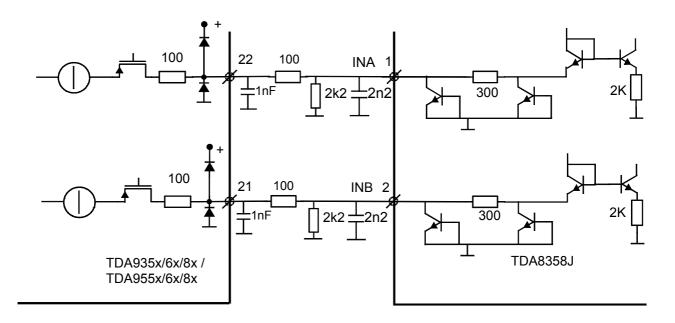

The input circuit is a differential voltage driven input. The input circuit is specially designed for direct connection to TV signal processors delivering a differential signal, but it is also suitable for single-ended applications See 2.4.2. For processors with output currents, the currents have to be converted to voltages by the conversion resistors  $R_{CV1}$  and  $R_{CV2}$  connected to pins 1 INA and 2 INB. Some type numbers of suitable drive circuits: TDA9151B, TDA9160A, TDA9162, TDA933X, TDA8366, TDA8367, TDA837X, TDA884X/5X (one chip family), TDA886X/7X/8X (bocma family), TDA935X/6X/8X and TDA955X/6X/8X (ultimate one chip family) and TDA485X (deflection processor family).

An example of the vertical drive output signal of an "ultimate one chip" family IC is given below. The drive signal depends on which drive circuit is used. In the ultimate one chip family, the zoom is standard enabled and is set to a value of 25 (dec) on a range of 0 - 63. This causes a small flat piece just before the start of the scan.

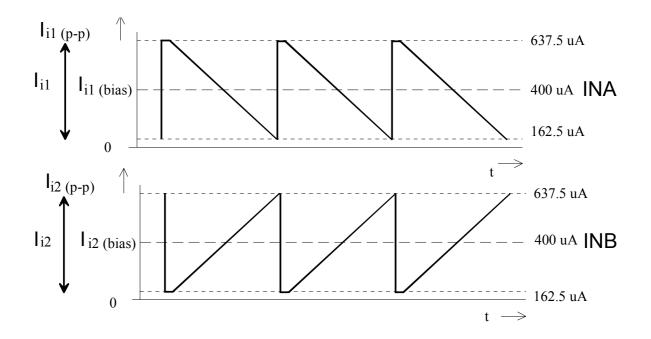

fig 5: Vertical drive output currents of the TDA935X/6X/8X / TDA955X/6X/8X family.

The bias output signal current is 400  $\mu$ A typical. The differential mode peak to peak output current is typical 475  $\mu$ A<sub>P-P</sub>.

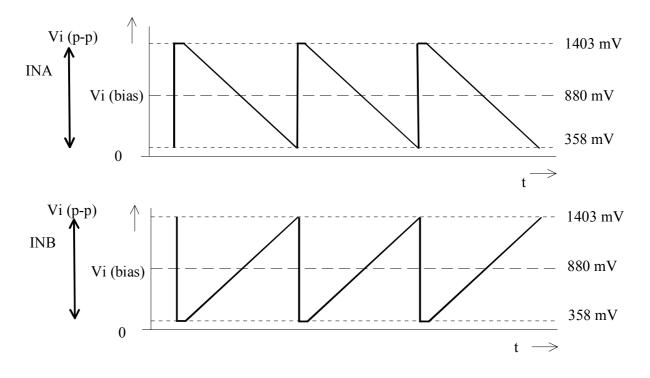

After connecting the TDA935X/6X/8X / TDA955X/6X/8X family to the TDA8358J, the following waveforms appear on the input pin 1 INA and pin 2 INB when the conversion resistors  $R_{CV1}$  and  $R_{CV2}$  are 2k2.

fig 6: Input voltages on pin 1 INA and pin 2 INB of TDA8358J.

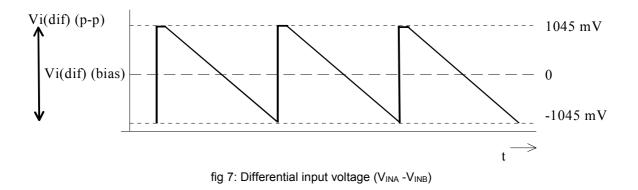

The differential voltage on the input  $(V_{INA} - V_{INB})$  is as follows:

The internal input configuration is symmetrical to have a good EMI behaviour, so the external input configuration should also be symmetrical. This means that the drive tracks should be as short as possible and routed next to each other.

The input configuration is as follows:

fig 8: Input configuration.

The differential input voltage is compared with the voltage across the measuring resistor  $R_M$ , providing the feedback information. The voltage across  $R_M$  is proportional to the output current. The relationship between the differential input voltage and the output current is defined by:

$$\begin{split} V_{i(dif)(p-p)} &= I_{o(p-p)} \times R_M \\ V_{i(dif)(p-p)} &= V_{INA} - V_{INB} \text{ (See fig 7.)} \end{split}$$

| V <sub>INA</sub>    | = voltage INA                                                               |

|---------------------|-----------------------------------------------------------------------------|

| V <sub>INB</sub>    | = voltage INB                                                               |

| I <sub>o(p-p)</sub> | = output current through the deflection coil and $R_M$ , peak to peak value |

| R <sub>M</sub>      | = measuring resistor                                                        |

|                     |                                                                             |

The next figure gives the vertical drive circuit diagram of the TDA935X/6X/8X / TDA955X/6X/8X family with the vertical output stage TDA8358J.

fig 9: Interconnect between TDA935x/6x/8x / TDA955x/6x/8x and TDA8358J

#### 2.4.1 Conversion resistors $R_{CV1,2}$ and measuring resistor $R_{M}$

Most of the TV signal processors of Philips have a current output. This current has to be converted by resistors  $R_{CV1}$  and  $R_{CV2}$  at the input of the TDA8358J.

The peak to peak input voltage  $V_{I(p-p)}$  should be as high as possible (maximum 1.5V) for an optimal reducing of the differential distortion on the input signals. So  $R_{CV1}$  and  $R_{CV2}$  have to be chosen so that  $V_{I(p-p)}$  is as high as possible. See fig 6. The maximum input voltage (bias + peak voltage) on pin 1 INA and pin 2 INB is 1.6V. The minimum input voltage (bias - peak voltage) is 100 mV, however a minimum input voltage of 300 mV is recommended because of an optimum linearity.

The conversion resistors  $R_{CV1}$  and  $R_{CV2}$  must have the same value and can be calculated by: (See fig 5 and fig 6)

$$R_{CV1,2} = \frac{V_{i(bias)} + V_{i(peak)}}{I_{i1,2(bias)} + \frac{I_{i1,2(p-p)}}{2}} \text{ or } R_{CV1,2} = \frac{V_{i(bias)} - V_{i(peak)}}{I_{i1,2(bias)} - \frac{I_{i1,2(p-p)}}{2}}$$

$\begin{array}{ll} V_{l(bias)} + V_{l(peak)} & = \mbox{ should be } < 1.5 \mbox{ for room for vertical alignment. (Maximum input voltage =1.6 \mbox{ } ) \\ V_{l(bias)} - V_{l(peak)} & = \mbox{ should be } > 0.3 \mbox{ for optimum linearity} \\ I_{1,2(p-p)} & = \mbox{ peak to peak output current given from the TV signal processor.} \\ I_{1,2(bias)} & = \mbox{ bias output current given from the TV signal processor.} \end{array}$

For the TDA935X/6X/8X or TDA955X/6X/8X family the value of  $R_{CV}$  is:

$$R_{CV1,2} = \frac{V_{i(bias)} + V_{i(peak)}}{I_{i(bias)} + I_{i(peak)}} = \frac{1.5}{400 + \frac{475}{2}} = 2350\Omega$$

So R<sub>CV1,2</sub> must be 2k2

The output current is adjustable up to 3.2  $A_{p-p}$  for the TDA8358J by varying  $R_M$ .

The measuring resistor  $R_M$  can be calculated by means of the formula:

$$R_{M} = \frac{V_{i(dif)(p-p)}}{I_{o(p-p)}}$$

$$V_{i(dif)(p-p)} = V_{INA} - V_{INB}$$

$$V_{i(dif)(p-p)} = I_{i1(p-p)} * R_{CV1} - (-I_{i2(p-p)} * R_{CV2})$$

Example for TDA8358J with the TDA935X/6X/8X or TDA955X/6X/8X family as TV signal processor:

We suppose the following:

$\begin{array}{ll} I_{O(p\text{-}p)} & = 2.4 \; A_{pp} \\ I_{i(p\text{-}p)} & = 475 \mu A \; (\text{value is given by TV signal processor}) \\ V_{i(p\text{-}p)} & = 1045 \; \text{mV} \; (\text{see fig 6}) \end{array}$

$$R_M = \frac{2.09V}{2.4A} = 0.87\Omega$$

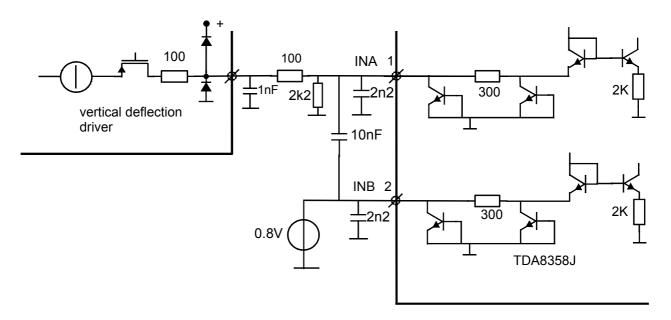

#### 2.4.2 Example of a single driven application with TDA8358J

It is also possible to drive the TDA8358J with a single drive signal, however differential driven is recommended. The single drive signal must be connected to pin 1 INA. Pin 2 INB needs then a stable DC voltage with a value of about the same as the bias voltage on pin 1 INA. A capacitor with a value of 10nF must be connected between pin 1 INA and pin 2 INB for stability. See fig 10. The measuring resistor  $R_M$  must be half the value of when the TDA8358J is differential driven. The value of the compensation resistor must be twice the value of when the TDA8358J is differential driven.

### TDA8358JN2 Vertical deflection output + East - West amplifier

### Application Note AN10114-01

fig 10: Example of a single driven application

#### 2.5 Feedback Circuit

#### Pin 12 FEEDB

#### fig 11: Feedback circuit.

The feedback circuit is built up with a reference between pin 4 (OUTB) and pin 12 (FEEDB), the voltage across  $R_M$  and a series resistor  $R_S$  (pin 12). The input circuit is connected to a differential V/I converter, which compares the voltage across  $R_M$  and the voltage across the internal conversion resistor  $R_{CON}$ . If both voltages are not equal the V/I converter drives the output stages until the voltage across  $R_M$  is equal to the voltage across  $R_{CON}$ .

#### 2.5.1 Series resistor (R<sub>s</sub>)

The purpose of the series resistor  $R_s$  at pin 12 FEEDB is to achieve equal impedance for the V/I converter,  $R_s = R_{con}$  because the V/I converter, see fig 11, should see equal input impedance at both inputs. This improves the common mode suppression. The tracks to the inputs are not the same. One track is connected internally to resistor  $R_{CON}$ . The other input has an external wire. To match  $R_{con}$ , the series resistor  $R_s$  is connected between the deflection coil and pin 12. Choose the value of  $R_s$  about 2.7k $\Omega$ .

If the output waveform should contain some oscillations, the value of  $R_s$  can be slightly changed. A small capacitor of 1pF-100pF between pin 12 (FEEDB) and pin 4 (OUTB) could also help to suppress minor oscillations.

#### TDA8358JN2 Vertical deflection output + East - West amplifier

#### 2.6 Vertical output stage

#### Pin 4 OUTB and pin 10 OUTA

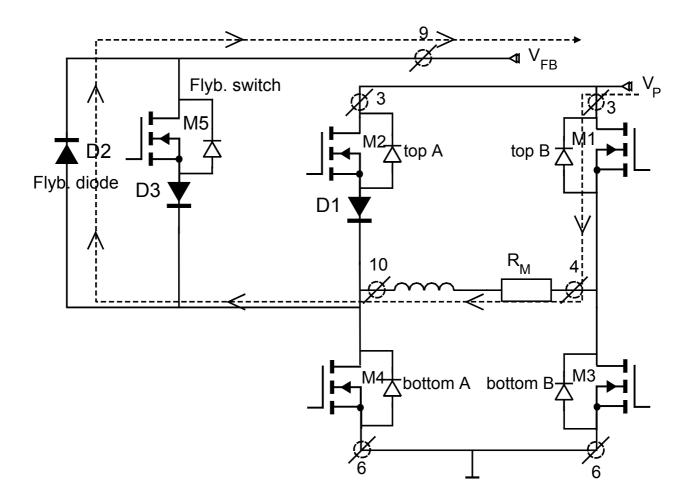

The Philips TDA8358J vertical output stage uses a class G bridge concept. (see fig 12). In the class G concept the flyback supply voltage can be chosen independent from the main supply voltage. This allows a very efficient DC coupling of the vertical output stages. This matches perfectly with modern driving circuits, which can change settings like amplitude, shift, slope and s-correction, which are controlled via the  $I^2C$  bus. The vertical deflection coil in series with resistor  $R_M$  is connected between the two outputs pin 10 OUTA and pin 4 OUTB. Resistor  $R_M$  is used to measure the current through the coil. The voltage across resistor  $R_M$  is the input voltage for the feedback stage.

The two output amplifier stages A and B are nearly identical. Output stage top MOSFET A (M2), diode D1 and bottom MOSFET B (M3), conduct for the first part of the sawtooth (coil) current and are supplied from the main supply ( $V_P$ ). Output stage top MOSFET B (M1) and bottom MOSFET A (M4) conduct for the second part of the sawtooth current and are also supplied via the same main supply voltage.

MOSFET (M5) is the flyback switch. It is supplied through a higher supply voltage ( $V_{FB}$ ) than the main supply voltage to achieve a short flyback time.

The maximum allowed values of the main supply voltage is 18 Volt and for the flyback supply voltage 66 Volt.

To prevent a short circuit between the main supply and the flyback supply, a diode (D1) is placed in series with the top MOSFET A (M2) of the output stage. To prevent conduction of the parasitic diode of the flyback switch (M5), (during the first part of the flyback period) a diode (D3) is placed in series with it.

fig 12: Output configuration TDA8358J.

## TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

The current flow through the output MOSFETs and the vertical deflection coil can be considered in four different parts/stages: the first part of the vertical scan, the second part of the vertical scan, the first part of the flyback and the second part of the flyback. The first and second part of the vertical scan will be discussed in this section, while the flyback part will be explained in the next section (2.7)

The current path in the vertical output bridge for the first part of the scan is illustrated by the dotted line in fig 13.

In this figure one can see that the current flows from the main supply pin via top MOSFET A (M2) and diode (D1) of output A in the vertical deflection coil and measuring resistor  $R_M$ , via bottom MOSFET B (M3) of output B to ground.

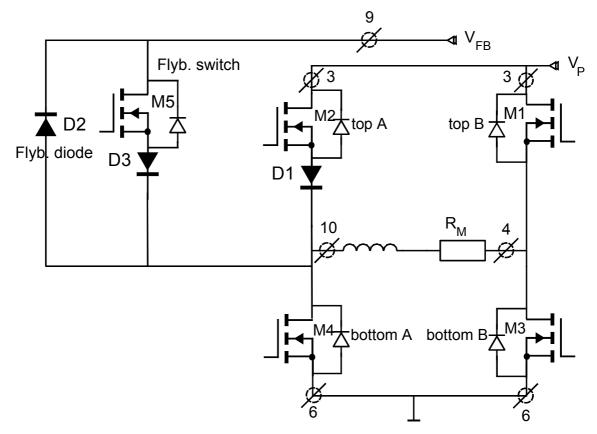

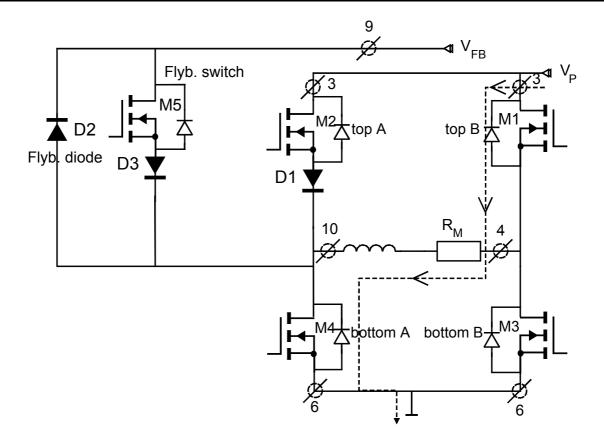

fig 13: Current path in first part of scan.

fig 14: Current path in second part of scan.

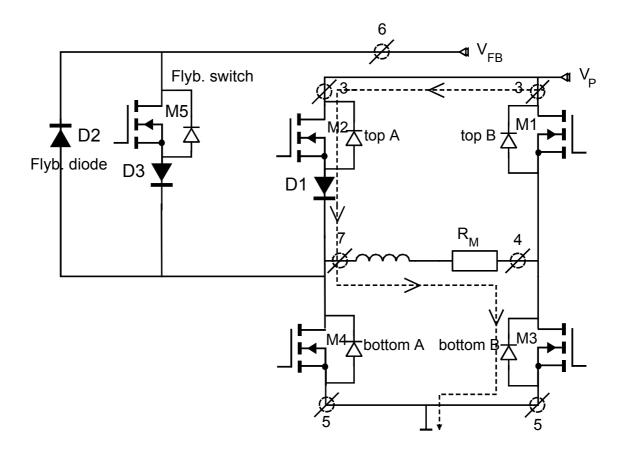

The current path for the second part of the scan is illustrated by the dotted line in fig 14. During the second part of the scan time, the current flows from the main supply pin via top MOSFET B (M1) via output B in the measuring resistor  $R_M$  and the vertical deflection coil, via bottom MOSFET A (M4) of output A to ground. During the scan time, the current that flows through the deflection coil has a sawtooth shape and the main supply (V<sub>P</sub>) supplies the current that is needed.

The supply current will be at it's maximum at the start of the scan, decreasing to the middle of the scan and than increasing until the end of the scan.

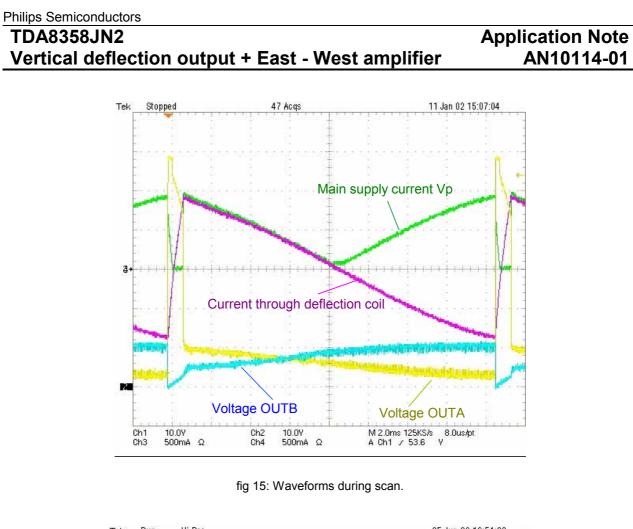

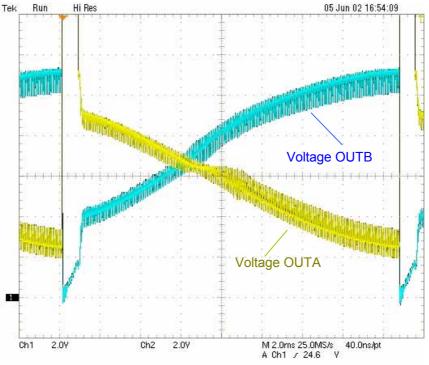

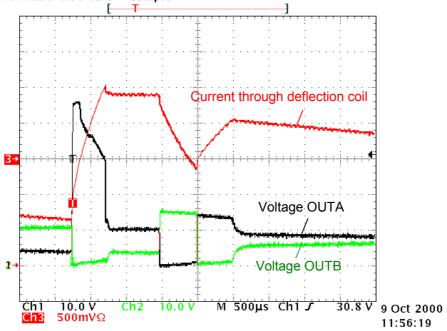

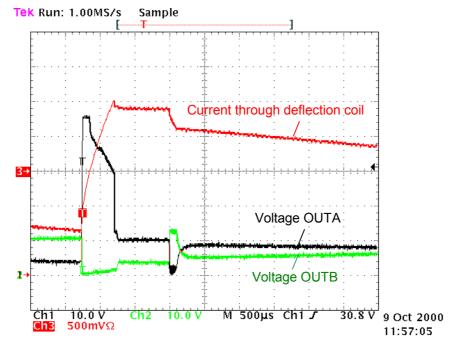

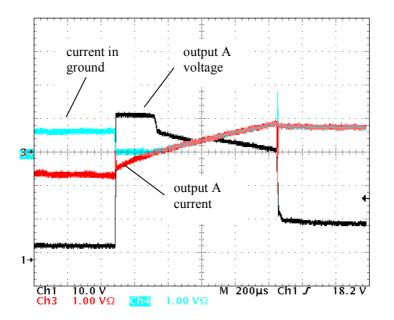

In fig 15 and fig 16 waveforms during scan are shown, these pictures are made with a digital oscilloscope. In fig 16 it is seen that the lines of output voltages A and B contain a small jump, when switching from the first part of the scan to the second part of the scan. This is because diode D1 causes a voltage drop. This is not crossover. The line of the output current is linear.

Furthermore one can see that the lines of the Output A voltage and the Output B voltage do not cross in the <u>middle</u> of the scan time. This is because the voltage drop across the deflection coil, for the first part of the scan is different than the voltage drop across the deflection coil during the second part of the scan. This is caused by the coil impedance, which exists of a resistive part and an inductive part. So the total voltage drop across the deflection coil exists of a resistive voltage and an inductive voltage. For the first part of the scan the inductive contribution and the resistive contribution are of opposite sign, while for the second part of the scan the inductive contribution and the resistive contribution have the same sign. See also section 2.11.1.

So, if the deflection coil has a *relatively large* L (inductance), the voltage drop during the *first part* of the scan has a *lower value* compared to the value of the second part of the scan. That's why the crossing point of the lines of output A and output B shifts to the left, when the L of the vertical deflection coil increases.

fig 16: Jump in output voltage

#### TDA8358JN2 Vertical deflection output + East - West amplifier

#### 2.7 The flyback switch

#### Pin 9 V<sub>FB</sub> and pin 10 OUTA

In the TDA8358J concept the value of the supply voltage ( $V_P$ ) and the flyback supply voltage ( $V_{FB}$ ) can be chosen independently (class G). In general, the flyback supply voltage will be chosen much higher than the supply voltage that is needed for the scan. A ratio of 2 to 4 is possible, with a maximum of 66 Volt. This is much higher than the value that is reached in conventional designs with a flyback voltage generator circuit (in general a ratio of 2, maximum). The flyback supply voltage is almost fully available at the output pin of stage A, thus across the deflection coil.

At the end of the scan time the input drive voltage will change fast in direction. The coil will try to maintain the present current level. At this moment the output signal cannot follow the input signal, which forces the amplifier into an open-loop condition. The flyback pulse will start.

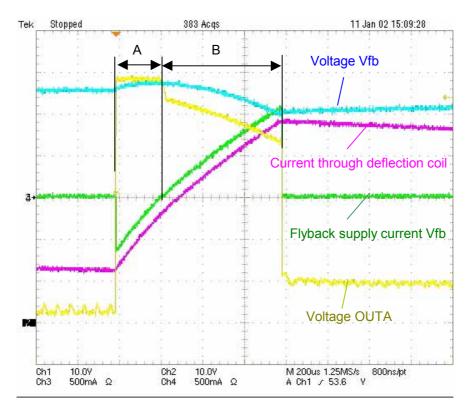

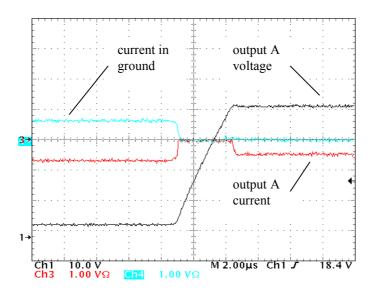

The flyback can be divided in part A and B, see fig 17. Due to the high voltage across the coil and the influence of the damping resistor, the first part A has a short duration. Part A ends when the current in the deflection coil becomes zero.

fig 17: Waveforms during flyback.

fig 18: Current path in first part of flyback.

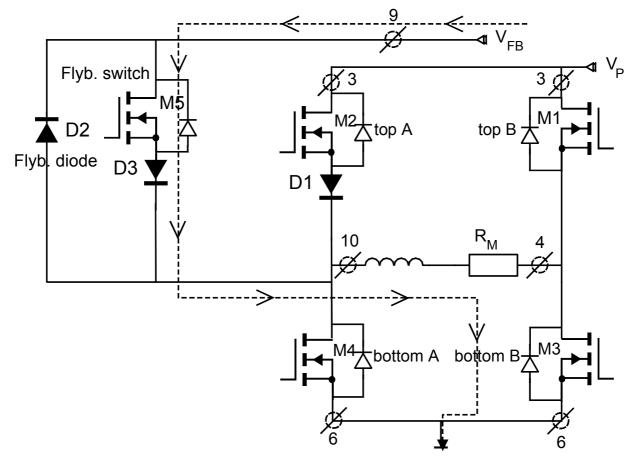

At the start of the first part of the vertical flyback the internal drive signal switches off the top MOSFET of stage B (M1).

The current in the deflection coil seeks a way out and the voltage at the output pin 10 OUTA increases and so the voltage at pin 4 OUTB will drop and tries to go below zero. Now, a clamp circuit is activated to keep this voltage above zero. This clamp which will switch-on again MOSFET M1, otherwise the parasitic diode across bottom MOSFET M3 would conduct which could cause substrate-currents which could cause a malfunction of the device.

The voltage at the output (pin 10) increases and the flyback diode D2 conducts. This output voltage becomes about 2 Volt higher than the flyback supply voltage (=voltage across diode D2), see fig 17. The current is fed into the flyback supply capacitor.

The current goes now through the top MOSFET of stage B (M1), the external measuring resistor  $R_M$ , the deflection coil and the internal flyback diode (D2) into the flyback supply, see the dotted line in fig 18.

The current flow for the second part "B" of the vertical flyback is given below.

fig 19: Current path in second part of flyback.

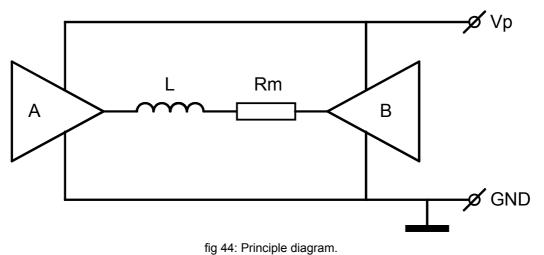

The second part, part B of the flyback pulse, starts when the current in the deflection coil crosses the zero level, see fig 17. Now, the current in the deflection coil is supplied by the flyback voltage supply and the flyback switch (M5) conducts. The current flows via the flyback switch (M5), the internal diode (D3), the deflection coil, the measuring resistor  $R_M$ , via the bottom MOSFET of stage B (M3) to ground, see fig 19. (Due to a voltage loss across the flyback switch (M5) + the internal diode (D3), the output voltage at pin 7 is about 8 V lower than the flyback supply voltage. This voltage drop depends on the current in the coil; a higher current means a higher loss and thus a higher voltage drop.

The current through the coil will become positive now and will increase until the voltage value measured across  $R_M$  equals the input voltage. Then the feedback loop is closed and the flyback switch is switched off. The scan sequence can start again.

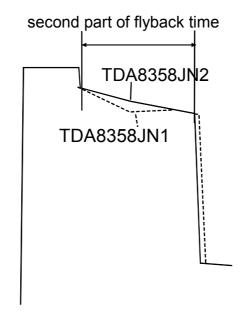

#### 2.7.1 Adaptive control of the flyback switch

The waveform during part B of the flyback waveform has a shape that is created by the adaptive control of the flyback switch, which operates as follows. The output current of the flyback switch is measured on a certain level onwards, the drive of the flyback switch is increased, thus lowering the impedance of the flyback switch at increasing flyback current.

In the TDA8358JN2 the adaptive control circuit is activated at all values of the output current. This results in a lower dissipation in the flyback switch and a somewhat shorter flyback time. In the TDA8358JN1 the adaptive control circuit is <u>not</u> activated at a low output current. The small difference in the output voltage is given in fig 20:

fig 20: Small difference in output voltage (flyback pulse) between N1 and N2

#### 2.8 Damping resistor R<sub>D1</sub> and damping resistor compensation circuit

#### Pin 13 COMP

fig 21: Damping resistor compensation.

#### 2.8.1 Damping resistor R<sub>D1</sub>

A damping resistor is connected across the deflection coil to smooth the switch points of the current and voltage as well to prevent ringing. The value of  $R_{D1}$  depends on the deflection coil and it should be as high as possible. Choose the value of  $R_{D1}$  about 270 $\Omega$ . Be aware that there can be a damping resistor mounted on the deflection coil on the picture tube.

If the damping resistor is situated on the deflection coil on the picture tube, the following picture fig 22, is seen *by measuring the current through the wires from the PCB to the deflection coil connector* (point P in fig 21). The damping resistor causes the difference in current values between points P and Q during flyback. During the flyback time period a higher current flows through the damping resistor than during scan time due to a higher voltage across the deflection coil.

If the value of the damping resistor is too high, the peak to peak voltage of line frequency ripple on the vertical output voltage will be too high. The impedance of the deflection coil is higher than the value of the damping resistor.

fig 22: Current through deflection coil measured on point P, Q and R in fig 21.

#### 2.8.2 Damping resistor compensation circuit

The current values in the damping resistor  $R_{D1}$  during scan and flyback are significantly different. During the flyback time period a higher current flows through the damping resistor due to a higher voltage across the deflection coil. For example with  $V_{FB}$  = 55V and  $R_{D1}$  = 300 $\Omega$ , the current through  $R_{D1}$  during flyback time is 55V/300 $\Omega$  = 183mA. With a main supply voltage  $V_P$  of 14V, the current through  $R_{D1}$  during scan time is 14V/300 $\Omega$  = 47mA. Both the damping resistor current and the deflection coil current flow into the measuring resistor  $R_M$ . During flyback time the current in the measuring resistor  $R_M$  is higher then the intended current in the deflection coil. So a too low current flows into the deflection coil compared to the input signal during flyback time. This has an influence on the time the flyback switch is conducting. So without compensation the flyback switch stops conducting too soon and the flyback pulse width is too small. Now it will take a rather long time to reach the output current which equals the input signal. This results in a too low deflection coil current at the start of the scan.

The differences in the damping resistor current values during scan and flyback have to be compensated in order to achieve a short settling time. For that purpose a compensation resistor is connected between pin 10 OUTA and pin 13 COMP. See fig 21.

#### 2.8.3 Calculation of the compensation resistor $R_{\mbox{\tiny CMP}}$

The value of the compensation resistor depends on:

- The flyback voltage supply; V<sub>FB</sub>

- The internal voltage loss of the current path between pins V<sub>FB</sub> and OUTA. So the voltage loss across the flyback switch M5 and diode D3; V<sub>loss(FB)</sub>. See fig 19.

- The voltage of the main supply voltage;  $V_P$ .

- The value of the damping resistor; R<sub>D1</sub>

- The value of the series resistors on pin 12 FEEDB; R<sub>S</sub>

- The peak to peak output current; I<sub>o(p-p)</sub>

- The value of the deflection coil resistance in hot condition = R<sub>coil(cold)</sub> × 1.2

- The value of the measuring resistor;  $R_M$

## TDA8358JN2Application NoteVertical deflection output + East - West amplifierAN10114-01

The compensation resistor  $R_{CMP}$  is calculated in the following way:

$$R_{CMP} = \frac{\left(V_{FB} - V_{loss(FB)} - V_{P}\right) \times R_{D1} \times \left(R_{S} + 300\right)}{\left(V_{FB} - V_{loss(FB)} - \frac{I_{o(p-p)}}{2} \times R_{coil(hot)}\right) \times R_{M}}$$

Example of calculating  $R_{CMP}$ :

$\begin{array}{ll} V_{FB} &= 30V \\ V_{Ioss(FB)} &= 8V \\ V_{P} &= 14V \\ R_{D1} &= 270\Omega \\ I_{o(p\text{-}p)} &= 2.4A \\ R_{coil(hot)} &= 6\Omega \ x \ 1.2 = 7.2\Omega \\ R_{M} &= 0.87\Omega \\ R_{S} &= 2.7k\Omega \end{array}$

$$R_{CMP} = \frac{(30 - 8 - 14) \times 270 \times (2700 + 300)}{\left(30 - 8 - \frac{2.4}{2} \times 7.2\right) \times 0.87} = 447\Omega$$

In the formula, only the voltage loss of the flyback switch is taken into account, but there is also a small voltage loss in output stage B. To correct the calculated value that is a little bit too high, round off the value downwards by means of choosing the next lower value in the E-range. So:  $R_{CMP} = 390 k\Omega$ .

## So when a TV chassis used with different picture tubes with different $I_{o(p-p)}$ and $R_{coil}$ , the value of $R_{CMP}$ has to be adapted with each picture tube.

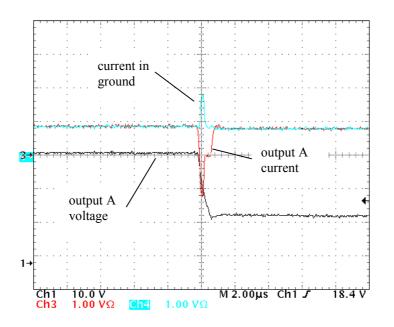

In fig 23, fig 24 and fig 25 are some oscilloscope pictures of an application, for different values of  $R_{CMP}$ . Pay attention to the differences in flyback time.

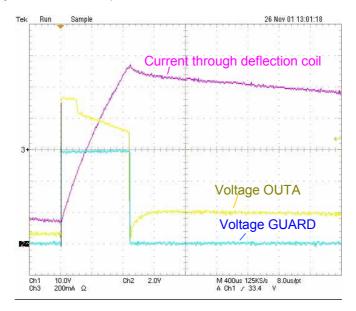

fig 23: Correct value of R<sub>CMP</sub>.

In fig 23, the value of  $R_{CMP}$  is correct. The result is a correct waveform of the coil current, output voltage and the vertical guard. The flyback time is 800  $\mu$ s.

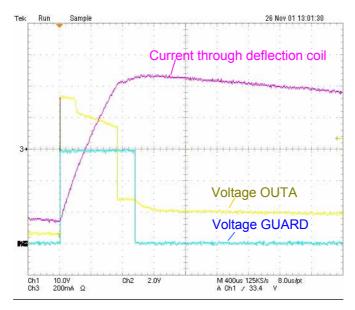

fig 24: R<sub>CMP</sub> too low, current overshoot at start scan / end flyback, too much compensation.

In fig 24 the value of  $R_{CMP}$  is too low. The result is an overshoot condition in the output current and longer flyback time than in fig 22 (900  $\mu$ s). Also the active high time of the vertical guard is longer than in fig 22.

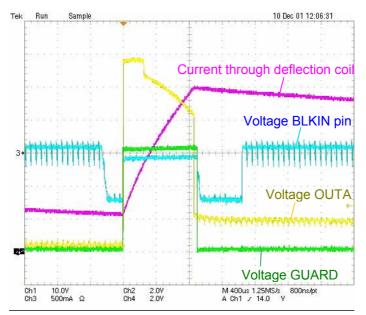

fig 25:  $R_{CMP}$  too high, current undershoot at start scan / end flyback, too less compensation.

In fig 25 the value of  $R_{CMP}$  is too high. The result is an undershoot condition in the output current and clipping of the output voltage to the supply voltage V<sub>P</sub>. The output current has not yet reached the level as given by the input signal, this is similar to an open loop condition and the vertical guard remains high. So the active high time of the vertical guard is longer (1000  $\mu$ s).

## Be aware that when $R_{CMP}$ does not have the correct value, the vertical guard signal of pin 11 GUARD has a different active HIGH time in comparison with the flyback time.

#### 2.9 Protection Circuits

The output circuit contains protection circuits for:

- Too high die temperature.

- Overvoltage of output A.

#### 2.9.1 High die temperature

A temperature sensor is located on the die of the TDA8358J. If this sensor detects a temperature of approximately 170 °C, the protection circuit activates. The protection circuit reduces the drive of the output stage and the current through the coil is reduced. The guard output becomes high and can be used to signal the TV signal processor that a fault condition occurred.

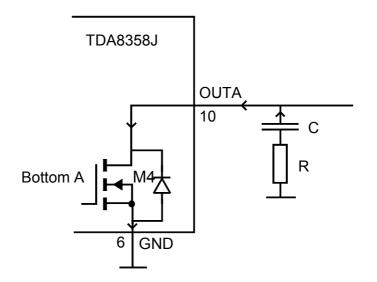

#### 2.9.2 Overvoltage output A

The overvoltage protection is activated, when the voltage of output stage A (pin 10 OUTA) increases above 70 Volt. During this condition, the protection circuit switches on MOSFET (M4) of output stage A, so M4 conducts and the output voltage at pin 10 OUTA decreases.

To prevent a short-circuit between pin 9  $V_{FB}$  and pin 10 OUTA, at active overvoltage protection, the flyback switch M5 is prevented to conduct.

Output stage B is 'self-protecting' because if an over-voltage occurs at output stage B (pin 4 OUTB), the parasitic diode from the top MOSFET (M1), conducts and the current is led to the elco at pin 3  $V_P$ . (This is not possible at output stage A, because diode D1 would block the current path to the elco at pin 3  $V_P$ )

#### 2.10 Vertical Guard Circuit

#### Pin 11 Guard

The TDA8358J has an internal vertical guard circuit, which delivers the guard signal to output pin 11 GUARD. This vertical guard circuit generates a pulse during every vertical flyback and at other conditions when the picture tube should be blanked. It can also be used to prevent the picture tube from burn-in, (due to faulty vertical deflection conditions) and as a vertical synchronisation signal to a microprocessor for e.g. On Screen Display. This guard pulse can be monitored by the TV signal processor.

The guard output is active (high) for one of the following conditions:

- 1. During the vertical flyback period.

- 2. During an open-loop condition of the TDA8358J. The circuit of the TDA8358J can see an open loop condition e.g. when the output voltage is clipping to the supply voltage  $V_P$  or clipping to the ground level due to a too low value of  $V_P$  or due to a too high value of the compensation resistor  $R_{CMP}$ .

- 3. During thermal protection of the TDA8358J (See section 2.9.1)

The guard output stage is a current source. In most applications a load resistor on pin 11 GUARD is used. This load resistor is used for having a quicker fall time of the guard pulse.

Be aware that when the compensation resistor  $R_{CMP}$  does not have the correct value or the value of the main supply voltage  $V_P$  is too low, the vertical guard signal has a different active HIGH time in comparison with the flyback time.

2.10.1 Vertical guard with TDA935X/6X/8X/N2 / TDA955X/6X/8X family as TV signal processor circuit.

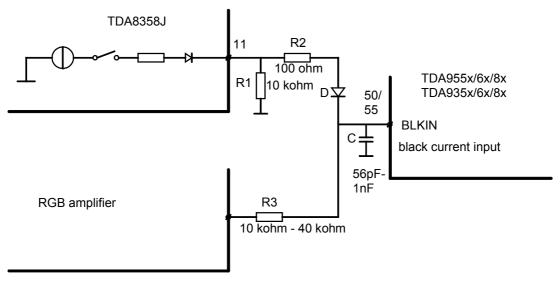

#### 2.10.1.1 Pin BLKIN of TV signal processor